Logic Design K-diagram [diagram] Activity Diagram Example

Digital logic design engineering electronics engineering Logic system design ktu chapter-4.ppt Answered: using k-map to reduce the logic circuit…

[Solved] HELP. Solve the following using K-map and design a logic

Solved q2) create k-map and logic circuit for the following Logic model template microsoft word [solved] help. solve the following using k-map and design a logic

Digital logic design engineering electronics engineering

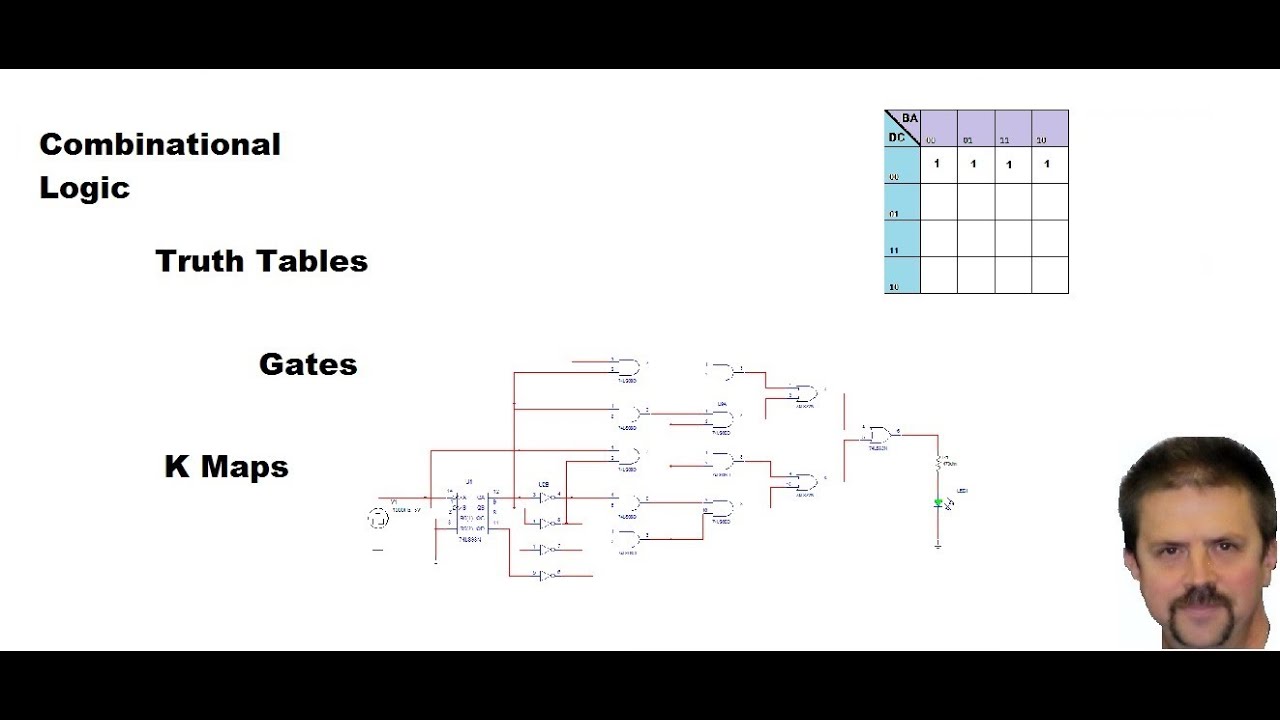

Solved using k-map, design a logic circuit to implement theLab 4 combinational logic design (k maps) Solved create logic diagram for: ko = a’ (logic gate: 1[diagram] k map logic diagram.

Howto kLogic symbols and intro to k-maps • anthony li Logic digital pos map sop using converting betweenSimply using k-map technique. for the below expression, draw the logic.

Solution: digital logic design (k-map, truth table, logic diagram

K mapSolution: digital logic design (k-map, truth table, logic diagram Logic digital pos map sop usingLogic show priority maps outputs inputs diagram encoders details d2 d3 di do solved transcribed text.

Solved: show the k-maps and logic diagram of a priority en...[solved] help. solve the following using k-map and design a logic Solved problem #5 use k-map to design a logic diagram toSolved 1. show the schematic of logic design circuit using.

Howto dash

Logic designLogic combinational maps using Module 2-k-mapLogic design (k-map) solve some questions.

Combinational logic design using k mapsDigital logic design engineering electronics engineering Solved a) referring to the logic diagram shown below, design[diagram] activity diagram example.

Solution: digital logic design k map

[solved] help. solve the following using k-map and design a logicSolution: digital circuit design combinational logic design using k map Solution: digital logic design (k-map, truth table, logic diagramSolution: digital circuit design combinational logic design using k map.

[solved] problem: design a logic diagram of the circuit (the circuitSolved: problem #2.) using k-map to reduce the logic circuit shown Pos map sop using converting between logic digital.